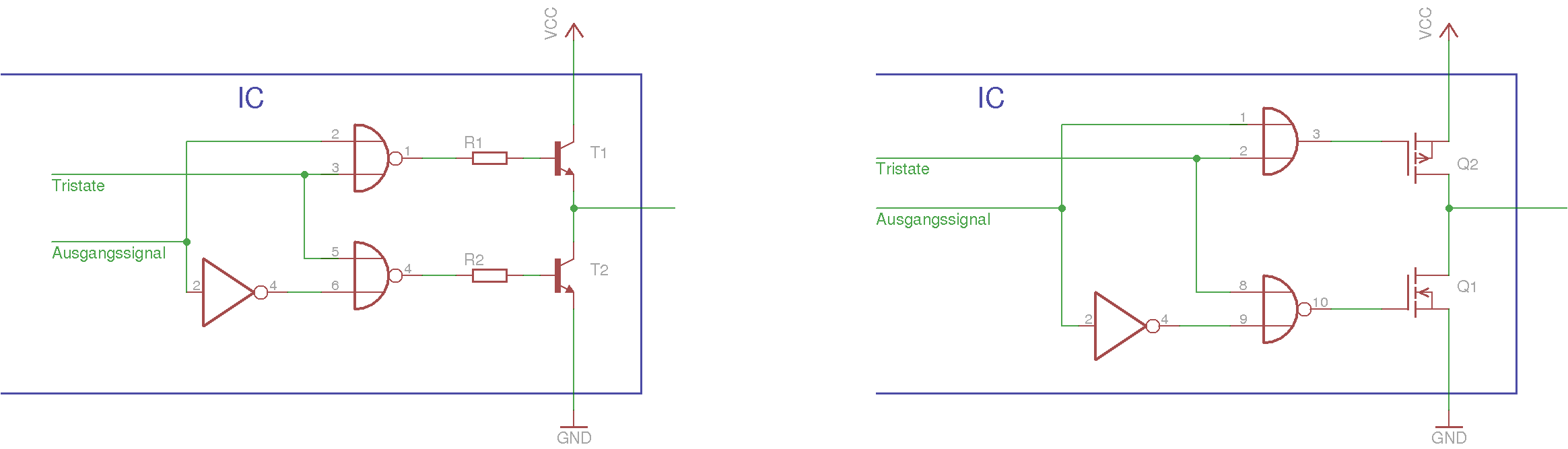

Is there a reason to choose BJTs over MOSFETs when using GPIOS?.Are the circuits equivalent? With that I mean, is there an extra functionality that the second design might achieve that I'm not seeing? or more broadly, I'm overlooking something?.Note2: Reduction of GPIOS might be achieved using an inverter (not gate) with GPIO1 and GPIO2 and shorting GPIO_01 and GPIO_OE2, thus having only a GPIO for enable/disable (~ enable/HIGH-Z) and other to switch between H and L. Note1: Switches S1, 2, 3, and 4 are just for simulation simplicity, not considered in the final design. In our design case, it has been further observed that the power optimization with clock gating techniques at RTL level saves 67.38%, Gate Level 67.29% & Power Driven around 68.79% of power while 30.38 %, 27.85 % &31.21% silicon area respectively have been saved.Here I don't attach a truth table since the simulated behavior is the same, only with more components. For designs that have large multi-bit registers, clock gating can save power and reduce the number of gates in the design. Clock gating reduces the clock network power dissipation, relaxes the datapath timing, and reduces routing congestion by eliminating feedback multiplexer loops. Clock gating is an important high-level technique for reducing the power consumption of a design. The use of custom SRAM in place of synthesizable flip flops in the input block has resulted in a saving of over 26% of the silicon area and power optimization is 65% when operated at 16 ns clock. The other two components of the routing node take up negligible area in comparison. Of the four components of routing node, the input block (mainly consisting of buffers) and scheduler have been modified to save area requirements. Resource sharing for on-chip network is critical to reduce the chip area and power consumption.An area efficient implementation of a routing node for a NoC is presented. Power consumption, area overhead and the entire NoC performance is influenced by the router buffers. Small optimizations in NoC router architecture can show a significant improvement in the overall performance of NoC based systems. Network-on-Chip (NoC) is the interconnection platform that answers the requirements of the modern on-Chip design. Post layout simulation showed that the new circuit provides the same functional performances as conventional solutions with significantly less power consumption, area and digital noise. The different flip-flops were implemented in STMicroelectronics 65 nm process technology and simulated for the worst case condition where the switching activity is maximal. To evaluate its performance, an octal flip-flop was built according to the new proposed structure and compared to the main octal flip-flops used today. A new n-fold flip-flop exploiting the clock gating technique for both outputs enabling and power saving is presented. In this paper we delve into the design of n-fold flip-flops with output enable. With the evolution of the semiconductor industry and the continuous growing demands for high performance VLSI circuit, the aggressive scaling in feature size and high integration density along with the high operating frequencies make power consumption and digital noise in modern analog and digital devices one of the top concerns of Very Large Scale Integration (VLSI) circuit design.

0 kommentar(er)

0 kommentar(er)